| 高速PCB訊號過孔分析 (1) : 電鍍通孔 (Plated Through Hole) PTH Via – HengeTek | 您所在的位置:网站首页 › pcb via孔改为pad孔 › 高速PCB訊號過孔分析 (1) : 電鍍通孔 (Plated Through Hole) PTH Via – HengeTek |

高速PCB訊號過孔分析 (1) : 電鍍通孔 (Plated Through Hole) PTH Via – HengeTek

|

隨著高速信號傳輸速率的提升演進,對於 PCB (Printed Circuit Board) 印刷電路板上的設計細節更要多加重視,其中使信號線在PCB各層之間相互連接的導通孔 Via,不僅僅只需考量到增加板內走線空間,而選擇使用 Via size 孔徑越小越好的過孔,還需要關注其過孔結構特性與綜合性能,選出適當的 Via 過孔來規劃 PCB layout 走線,使整塊電路板的 SI (signal integrity) 信號完整性質量得到保障,以達到最高的性能與成本效益。下面我們將透過一個 (14Layers / 1.6mm / PTH via ) 的過孔,來觀察 ( 0.1mm / 0.2mm / 0.3mm ) 不同尺寸的電鍍通孔 (Plated Through Hole) PTH via 在時域 (time domain) 與頻域 (frequency domain) 裡頭的特性表現。

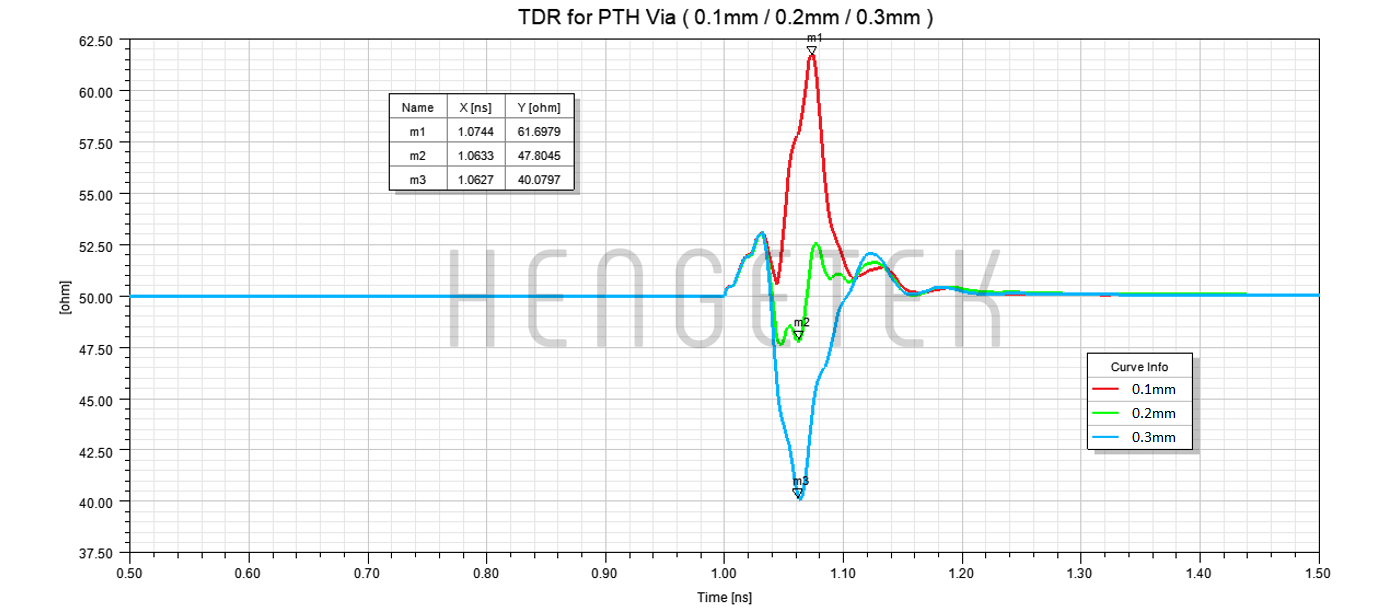

從時域反射計 TDR (Time-Domain Reflectometry) 曲線裡可以觀察到電鍍通孔 (Plated Through Hole) PTH via 在 (0.1mm / 0.2mm / 0.3mm) 不同孔徑下的阻抗峰值分別為 (61.69 ohm / 47.80 ohm / 40.07 ohm),其中孔徑 0.1mm Via 在此層疊結構 (layer stackup) 條件下與 50 ohm 傳輸線阻抗不連續性差異最大,其11.69 ohm 阻抗誤差已達到 23% ,而孔徑 0.2mm Via 和 0.3mm Via 阻抗誤差也分別為 2.2 ohm (4.4%) 和 9.93 ohm (19.86%),由此可以發現並非所有應用場合皆適合小孔徑電鍍通孔 (Plated Through Hole) PTH via,且使用過大的 Via 過孔也非恰當的選擇。

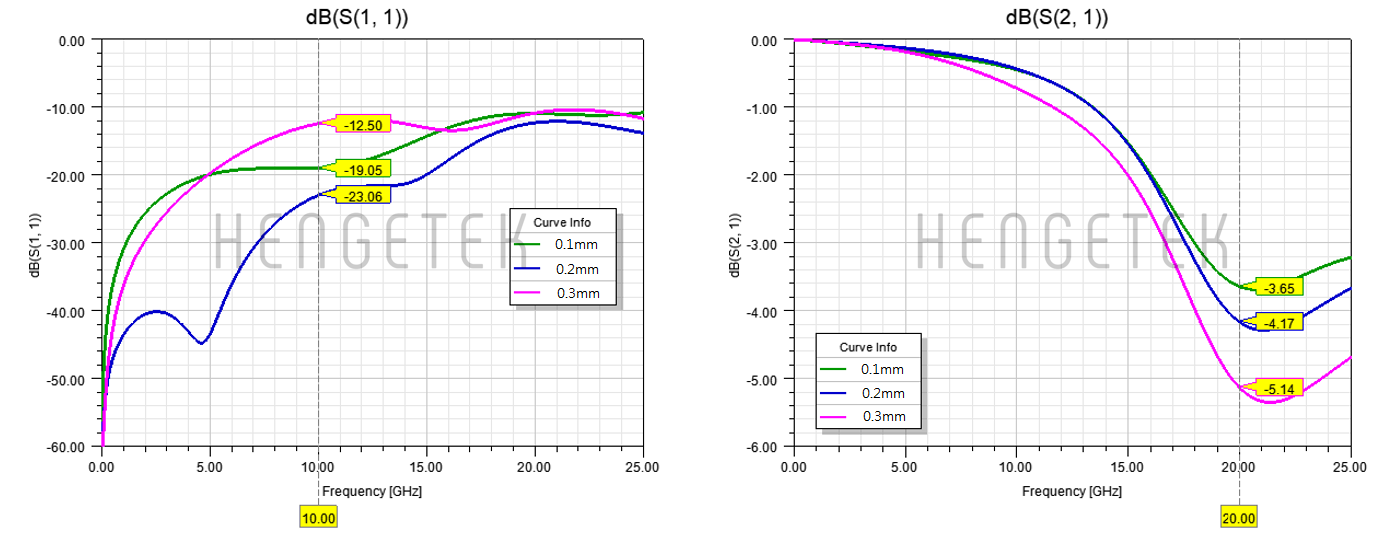

接著我們從頻域 (frequency domain) 的角度來觀察S參數裡各項性能。如S11回波損耗 (return loss) 曲線所示,在整個 25 GHz 頻段內不同孔徑的電鍍通孔 (Plated Through Hole) PTH via,其中 0.2mm PTH via 的S11回損趨勢最小,0.1mm 和 0.3mm PTH via 回損皆大了許多。 在接近 5 GHz 頻段的位置其 0.2 mm 對比 0.1 mm & 0.3 mm S11回損差了超過 20dB。隨著越往高頻走S11回波損耗 (return loss) 的差距也逐步縮小,在 10 GHz 頻段其 PTH via (0.1 mm / 0.2 mm / 0.3 mm) 分別落在 (-19.05dB / -23.06dB / -12.50dB)。 在S21插入損耗 (insertion loss) 的部分,低頻段 5 GHz 頻率範圍以下不同孔徑的S21插損曲線並沒有明顯的差距,隨著頻率的提升越往高頻走S21插損的趨勢逐漸顯現。在16 GHz 頻率以下 0.1mm & 0.2mm 孔徑的 PTH via 在S21插損曲線表現一致皆優於 0.3mm 孔徑,超過 16 GHz 頻率以上孔徑越粗S21插損越差。在 20 GHz 頻率位置其 PTH via (0.1mm / 0.2mm / 0.3mm) 分別為 (-3.65dB / -4.17dB / -5.14dB),最小孔徑 0.1mm PTH via 插損最小,0.3mm PTH via 插損最大。 經由時域 (time domain) 與頻域 (frequency domain) 兩個角度所觀察到的結果,孔徑最小的 0.1mm 電鍍通孔 (Plated Through Hole) PTH via 雖然可以增加整塊 PCB (Printed Circuit Board) 印刷電路板的 layout 走線空間,但在此層疊結構 (layer stackup) 條件下,其 TDR 阻抗曲線峰值來到了 61.69 ohm 與 50 ohm 傳輸線阻抗不連續性差距最大誤差已達到 23%,這將導致高速信號經過此處 PTH via 位置產生不小的反射,使得 SI (signal integrity) 信號質量存在著風險。並且選用越小孔徑的 Via 也會增加 PCB 印刷電路板的製造成本,故 Via 過孔的選擇非越小孔徑越有優勢,還需依據具體的層疊結構 (layer stackup) 和信號帶寬範圍 (bandwidth) 與應用場景,來評估出最適當理想的 Via 過孔。 |

【本文地址】